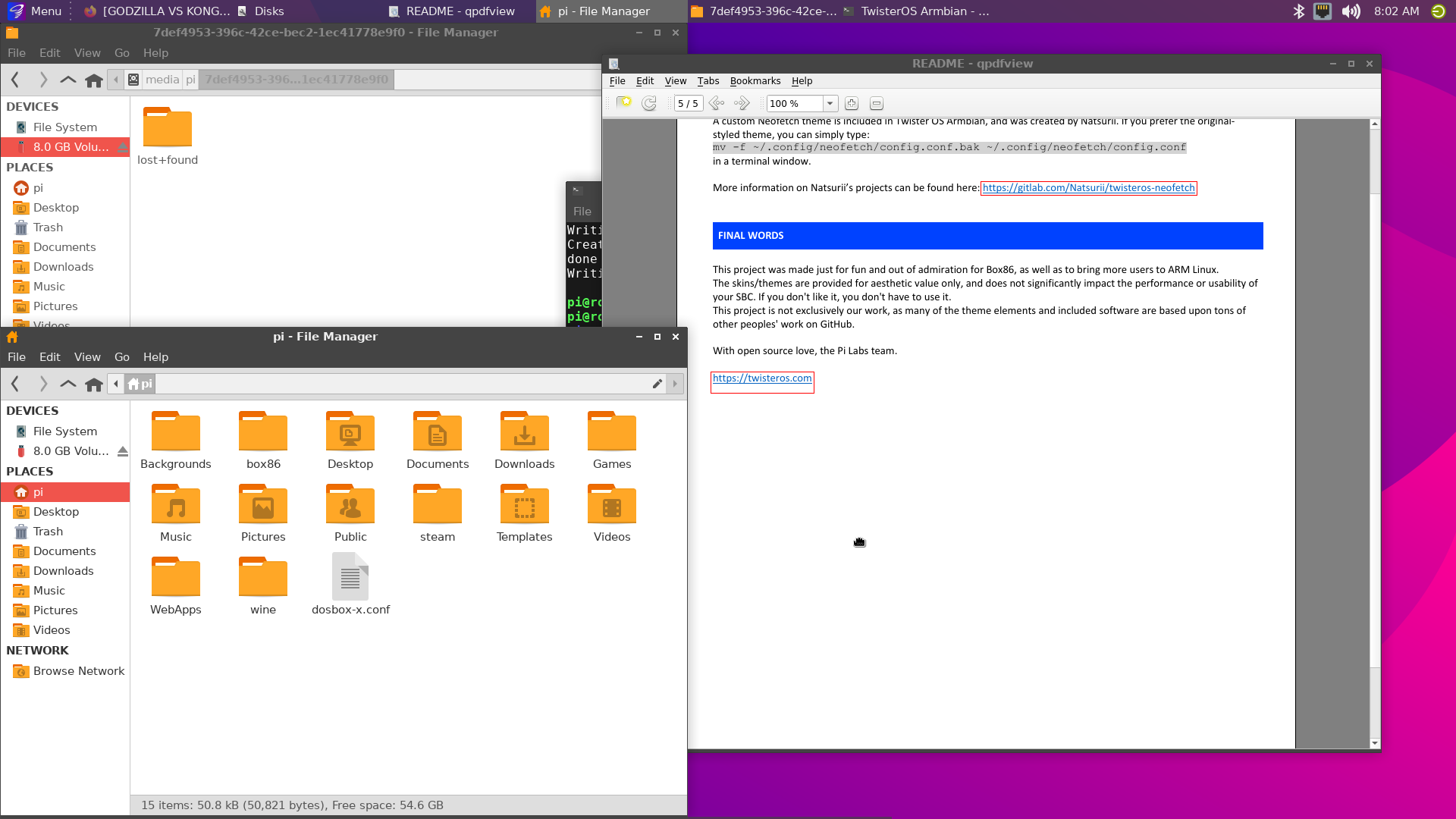

Neue Version 0.7.3

Soll gefixt sein.

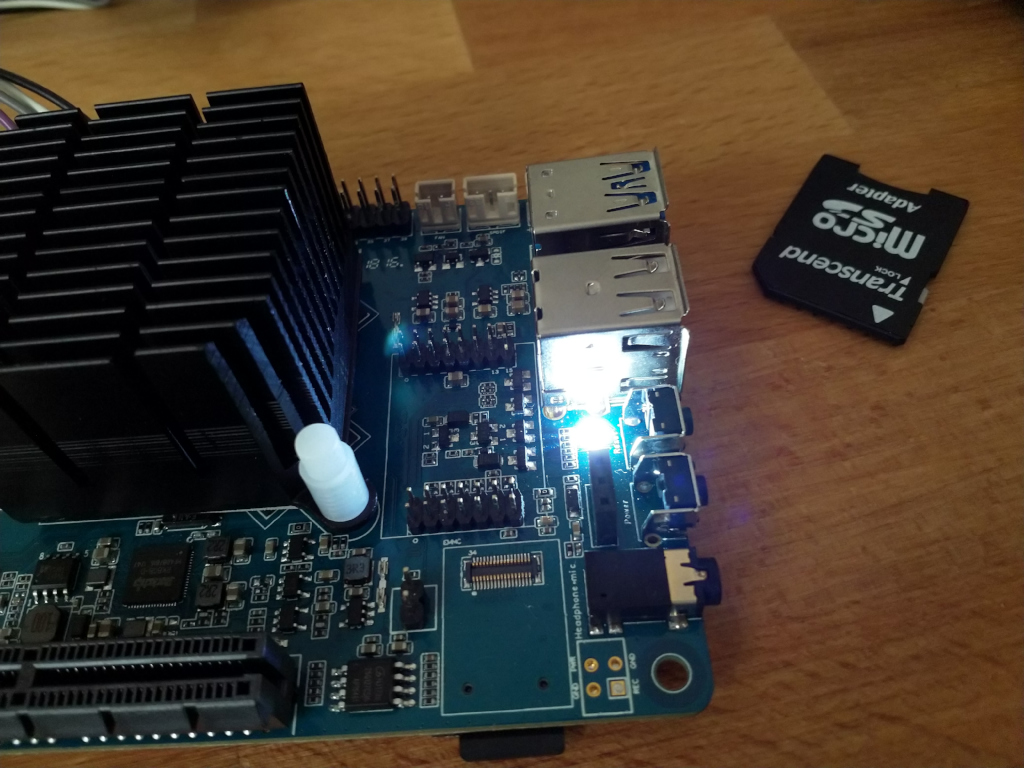

USB2/3

PCIe

LED's

LED's

Weiße LED starten nach dem Booten dauerhaft OK

PCIe

Treiber soll drin sein, aber die 3,3V werden nicht zur Karte durchgeschaltet. Somit funktioniert PCIe nicht.

Nicht OK

USB2

USB-Funkadapter wird erkannt

Bus 004 Device 001: ID 1d6b:0003 Linux Foundation 3.0 root hub

Bus 003 Device 001: ID 1d6b:0002 Linux Foundation 2.0 root hub

Bus 002 Device 002: ID 1113:3163 Medion AG

Bus 002 Device 001: ID 1d6b:0001 Linux Foundation 1.1 root hub

Bus 001 Device 001: ID 1d6b:0002 Linux Foundation 2.0 root hub

Bus 006 Device 001: ID 1d6b:0001 Linux Foundation 1.1 root hub

Bus 005 Device 001: ID 1d6b:0002 Linux Foundation 2.0 root hub

Funktastur getestet OK

USB3

Angeschlossene SSD wird erkannt OK

Kurzer Speed-Test. Bitte dran denken, wir haben hier noch kein optimiertes Release, sondern einen ersten Gehversuch. Da sind noch ganz viele Dinge anzupassen, was sicherlich noch Wochen, wenn nicht Monate dauert! Also, die Messergebnisse mit der nötigen Vorsicht genießen. Und dran denken, wenn @tkaiser das Ding richtig untersucht, dann haben wir auch ordentliche Meßergebnisse!

Haupt-PC

2,5Zoll am USB3-Port

sudo dd if=/dev/zero of=sd.img bs=1M count=4096 conv=fdatasync

[sudo] Passwort für frank:

4096+0 Datensätze ein

4096+0 Datensätze aus

4294967296 bytes (4,3 GB, 4,0 GiB) copied, 38,171 s, **113 MB/s**

ROCKPro64

Ich benutze eine SAN Disk 240GB SSD an einem Inateck USB 3.0 2,5 Zoll Adapter.

Info zum USB-Adapter

lsusb

Bus 004 Device 002: ID 174c:55aa ASMedia Technology Inc. ASM1051E SATA 6Gb/s bridge, ASM1053E SATA 6Gb/s bridge, ASM1153 SATA 3Gb/s bridge

2,5 Zoll SSD am USB2-Port

sudo dd if=/dev/zero of=sd.img bs=1M count=4096 conv=fdatasync

4096+0 records in

4096+0 records out

4294967296 bytes (4.3 GB, 4.0 GiB) copied, 160.058 s, **26.8 MB/s**

2,5 Zoll SSD am USB3 Port

sudo dd if=/dev/zero of=sd.img bs=1M count=4096 conv=fdatasync

4096+0 records in

4096+0 records out

4294967296 bytes (4.3 GB, 4.0 GiB) copied, 36.2588 s, **118 MB/s**

Der @tkaiser erreicht deutlich höhere Geschwindigkeiten. Bis zu 400 MB/s. Hier nachzulesen.

Wenn ich so einen iozone Test mache wie der Thomas, dann erreiche ich ähnliche Werte

sudo iozone -a -g 1000m -s 1000m -i 0 -i 1 -r 16384K

Iozone: Performance Test of File I/O

Version $Revision: 3.429 $

Compiled for 64 bit mode.

Build: linux

Contributors:William Norcott, Don Capps, Isom Crawford, Kirby Collins

Al Slater, Scott Rhine, Mike Wisner, Ken Goss

Steve Landherr, Brad Smith, Mark Kelly, Dr. Alain CYR,

Randy Dunlap, Mark Montague, Dan Million, Gavin Brebner,

Jean-Marc Zucconi, Jeff Blomberg, Benny Halevy, Dave Boone,

Erik Habbinga, Kris Strecker, Walter Wong, Joshua Root,

Fabrice Bacchella, Zhenghua Xue, Qin Li, Darren Sawyer,

Vangel Bojaxhi, Ben England, Vikentsi Lapa.

Run began: Sat May 26 05:16:40 2018

Auto Mode

Using maximum file size of 1024000 kilobytes.

File size set to 1024000 kB

Record Size 16384 kB

Command line used: iozone -a -g 1000m -s 1000m -i 0 -i 1 -r 16384K

Output is in kBytes/sec

Time Resolution = 0.000001 seconds.

Processor cache size set to 1024 kBytes.

Processor cache line size set to 32 bytes.

File stride size set to 17 * record size.

random random bkwd record stride

kB reclen write rewrite read reread read write read rewrite read fwrite frewrite fread freread

1024000 16384 383912 348782 1515506 1659394

Da muss ich den Thomas nochmal was zu fragen. ??

UART2

Und zum Schluss ist mir noch aufgefallen, das die UART2 Schnittstelle jetzt funktioniert Ok, den Adapter, der morgen kommt, habe ich dann umsonst bestellt. LOL

OK