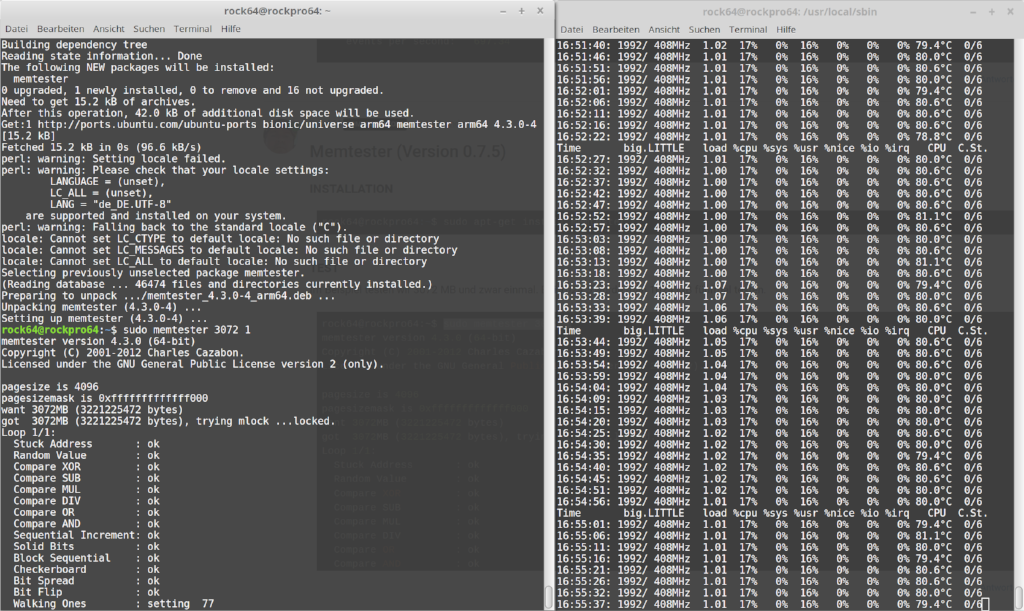

Heute das Ganze mal mit einer Samsung 860 Pro mit 256GB. Eingesetztes Filesystem ext4

rock64@rockpro64v2_1:/mnt$ uname -a

Linux rockpro64v2_1 4.4.132-1077-rockchip-ayufan-gbaf35a9343cb #1 SMP Mon Jul 30 14:06:57 UTC 2018 aarch64 aarch64 aarch64 GNU/Linux

Speedtest

rock64@rockpro64v2_1:/mnt$ sudo iozone -e -I -a -s 100M -r 4k -r 16k -r 512k -r 1024k -r 16384k -i 0 -i 1 -i 2

Iozone: Performance Test of File I/O

Version $Revision: 3.429 $

Compiled for 64 bit mode.

Build: linux

Contributors:William Norcott, Don Capps, Isom Crawford, Kirby Collins

Al Slater, Scott Rhine, Mike Wisner, Ken Goss

Steve Landherr, Brad Smith, Mark Kelly, Dr. Alain CYR,

Randy Dunlap, Mark Montague, Dan Million, Gavin Brebner,

Jean-Marc Zucconi, Jeff Blomberg, Benny Halevy, Dave Boone,

Erik Habbinga, Kris Strecker, Walter Wong, Joshua Root,

Fabrice Bacchella, Zhenghua Xue, Qin Li, Darren Sawyer,

Vangel Bojaxhi, Ben England, Vikentsi Lapa.

Run began: Tue Jul 31 14:27:17 2018

Include fsync in write timing

O_DIRECT feature enabled

Auto Mode

File size set to 102400 kB

Record Size 4 kB

Record Size 16 kB

Record Size 512 kB

Record Size 1024 kB

Record Size 16384 kB

Command line used: iozone -e -I -a -s 100M -r 4k -r 16k -r 512k -r 1024k -r 16384k -i 0 -i 1 -i 2

Output is in kBytes/sec

Time Resolution = 0.000001 seconds.

Processor cache size set to 1024 kBytes.

Processor cache line size set to 32 bytes.

File stride size set to 17 * record size.

random random bkwd record stride

kB reclen write rewrite read reread read write read rewrite read fwrite frewrite fread freread

102400 4 17896 23350 30390 31362 21611 14611

102400 16 56756 59180 86296 93819 51778 57327

102400 512 201347 221961 220840 222338 210887 230781

102400 1024 253752 273695 263884 266256 250153 273528

102400 16384 351112 356007 366417 372264 368721 356177

iozone test complete.

DD

Schreiben

rock64@rockpro64v2_1:/mnt$ sudo dd if=/dev/zero of=sd.img bs=1M count=4096 conv=fdatasync

4096+0 records in

4096+0 records out

4294967296 bytes (4.3 GB, 4.0 GiB) copied, 12.8358 s, 335 MB/s

Lesen

rock64@rockpro64v2_1:/mnt$ sudo dd if=sd.img of=/dev/null bs=1M count=4096

4096+0 records in

4096+0 records out

4294967296 bytes (4.3 GB, 4.0 GiB) copied, 11.4787 s, 374 MB/s

Fazit

Damit scheint der Adapter ganz gut am USB3.0 zu funktionieren. Die Schreibgeschwindigkeit ist ca. dreimal höher als mit der anderen SSD.